|

Mercredi 28 janvier 2026 - 10:43 |

| Translate |

|

| Rubriques |

| Réseaux sociaux |

|

| Liste des jeux Amiga |

|

| Trucs et astuces |

|

| Glossaire |

|

| Galeries |

|

| Téléchargement |

|

| Liens |

|

| Partenaires |

|

| A Propos |

|

| Contact |

|

|

|

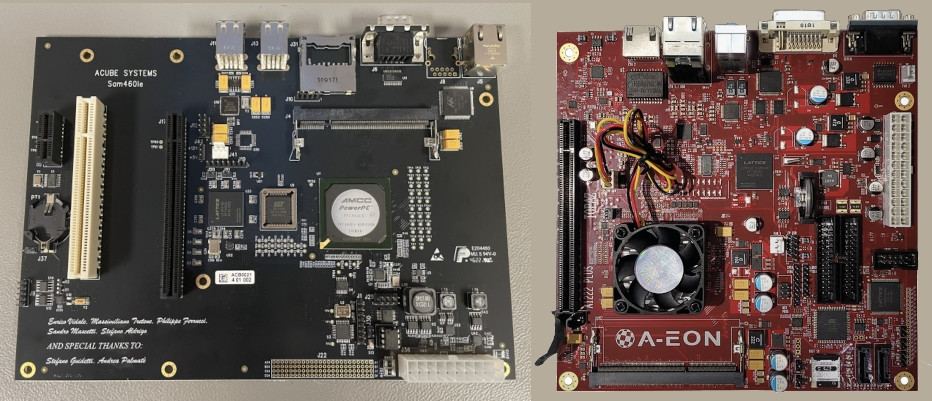

Sam460LE et A1222 Plus, un duel de poids léger

Aujourd'hui, début 2024, nous vivons une situation inhabituelle dans le monde Amiga NG. Nous avons le choix entre deux ordinateurs d'entrée de gamme : en 2023, ACube Systems a lancé une nouvelle version de la Sam460, nommée Sam460LE, et en 2024, après un long voyage plein de vicissitudes, AAA Technology a enfin introduit l'A1222 Plus.

La concurrence de deux ordinateurs de la même catégorie est quelque chose de complètement inhabituel dans le monde Amiga NG, c'est pourquoi il est souvent question de savoir lequel d'entre eux est le meilleur.

Explications des couleurs pour les tableaux :

| La couleur vert vif indique un avantage | La couleur turquoise indique un petit avantage | Le jaune indique un avantage possible à l'avenir | Et l'orange indique un inconvénient |

1. La carte mère

Lorsque l'on compare les cartes mères, une différence saute aux yeux :

la Sam460LE est au format Micro-ATX alors que l'A1222+ est Mini-ITX.

| Sam460LE | A1222 Plus | |

| Fabricant | ACube Systems Srl | AAA Technology sarl |

| Processeur | AMCC PowerPC 460EX | NXP QorIQ P1022 |

| Fréquence du processeur | 1,14 GHz | 1,2 GHz |

| Format | Micro-ATX | Mini-ITX |

| Micrologiciel | U-Boot | U-Boot |

| Mémoire | 2 Go de mémoire DDR2-400 | 8 Go de mémoire DDR3-800 |

| Ports d'extension | 1x PCIe v1.1 x4 (connecteur mécanique x16) 1x PCIe v1.1 x1 1x PCI v2.3, 32 bits/66 MHz | 1x PCIe v1.0a x4 (connecteur mécanique x16) |

| Ethernet | 1x GbE | 2x GbE |

| Coprocesseur | FPGA Lattice XP2 | Lattice LCMX02-640 |

| SATA | La Sam460LE n'en a pas, elle est généralement équipée de SATA I dans le port PCI | 2x SATA II (v2.6) |

| Audio | Pas de puce audio. Une carte audio est habituellement installée dans le port PCIe x1 | Codec Wolfson WM8776 I2S |

| Vidéo | - | Display Interface (DIU - interface d'affichage), résolution maximale de 1280x1024 en 24 bits, sans accélération matérielle |

| Systèmes d'exploitation | AmigaOS, MorphOS, Linux (Debian 8, Ubuntu 16.04) | AmigaOS, Linux (Debian 8, Ubuntu 16.04) |

| Port carte SD | Amorce possible du système d'exploitation à partir d'une carte SD | La carte microSD sert uniquement pour U-Boot |

La Sam460LE présente l'avantage de pouvoir être étendue plus facilement. Bien que les emplacements PCIe soient tous occupés dans une configuration normale, on peut installer un commutateur PCIe 1x1 -> 4x1 si nécessaire. Nous pouvons également installer MorphOS sur Sam460LE.

La carte mère de l'A1222+ est plus petite, dispose d'un contrôleur SATA II et de 8 Go de mémoire DDR3 (la mémoire au-delà de 2 Go sera utilisée par Linux et certaines applications AmigaOS). L'A1222+ présente aussi un autre avantage non mentionné dans le tableau, à savoir le système de fichiers NGFS. Il est plus moderne et plus rapide que SFS/02 et n'est actuellement utilisé que par les AmigaOne A1222+ et X5000. D'autres avantages comme la présence de deux ports Ethernet et un coprocesseur nettement plus puissant ne sont que théoriques, car AmigaOS ne peut pas encore les utiliser.

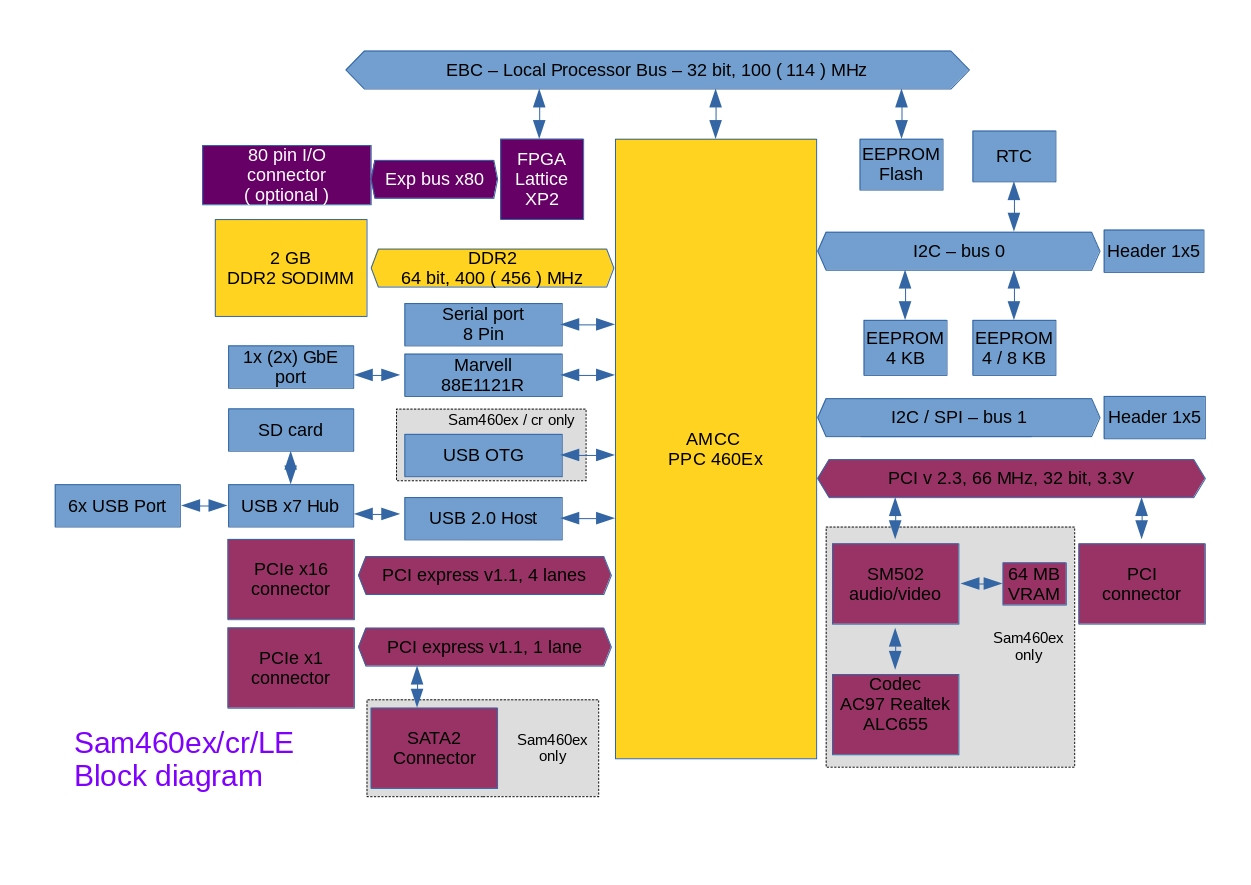

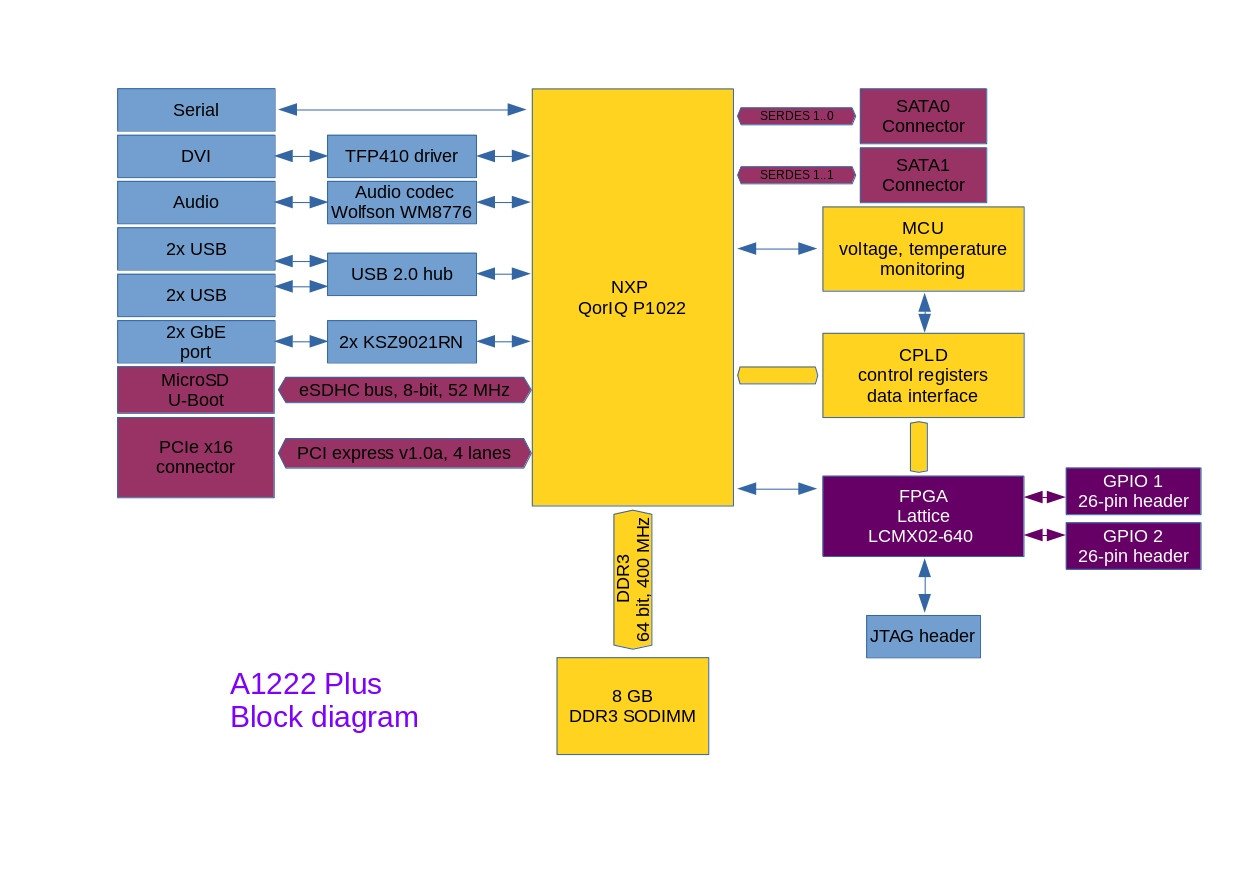

1.1 Schémas fonctionnels des ordinateurs

Le modèle Sam460ex original comprenait également un connecteur SATA II et une puce audio/vidéo avec accélération 2D. Les versions cr/LE n'en disposent plus, ces fonctions n'ont pas été utilisées en pratique.

Le coprocesseur Lattice est connecté au bus local du processeur (EBC, OPB, voir ci-dessous).

La carte SD est connectée en tant que périphérique USB et vous pouvez y installer des modules du noyau ou l'intégralité du système d'exploitation et démarrer directement à partir de celle-ci.

L'interface LCD de l'A1222+ fait partie du processeur et n'a pas d'accélération matérielle. Elle ne convient donc pas à un ordinateur de bureau. Elle pourrait être utilisée pour un serveur, lorsque l'on utilise l'interface LCD pour libérer un emplacement PCIe x4.

Le coprocesseur Lattice est connecté via le CPLD principal qui, en plus de communiquer avec le coprocesseur, contrôle par exemple la vitesse des ventilateurs. Le MCU surveille ensuite les tensions et les températures du processeur.

Le port microSD est connecté au contrôleur du processeur eSDHC. Il n'y a qu'un micrologiciel (U-Boot) sur la carte et il n'est pas accessible depuis le système. En théorie, cela pourrait être accessible avec un pilote adapté, la carte microSD contient une table de partition MBR, mais cela ne serait pas raisonnable. Nous pourrions facilement corrompre le micrologiciel par erreur.

À première vue, les deux ordinateurs sont assez similaires. Étant donné que les deux processeurs sont des "SOC" (System On Chip - système sur puce) et que la partie la plus importante de l'ordinateur se trouve donc à l'intérieur, ils méritent d'être examinés de plus près.

Puisqu'un simple examen des paramètres ne suffit pas, allons plus loin pour voir ce

qui se cache sous la surface. Donc au sein du processeur...

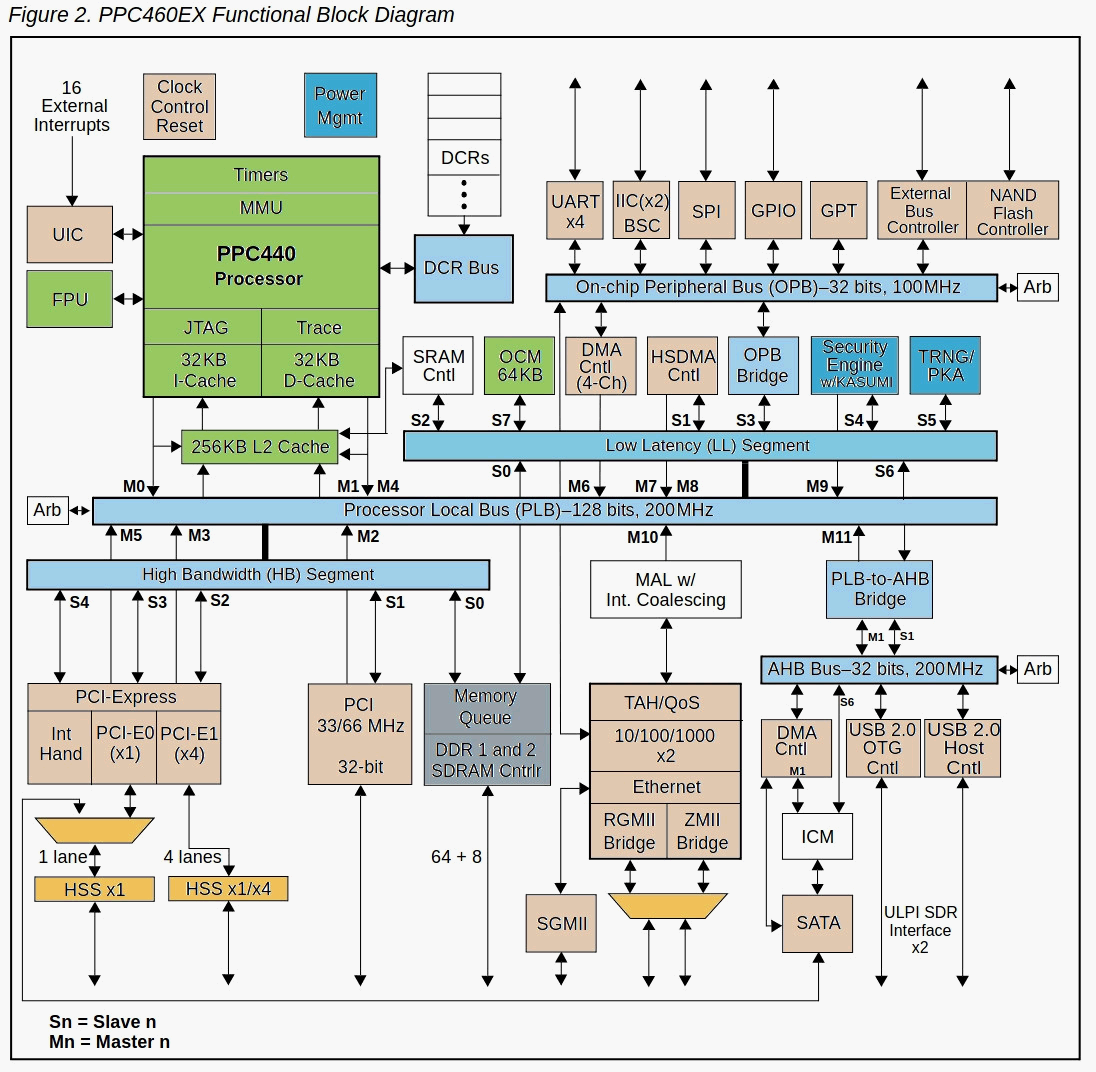

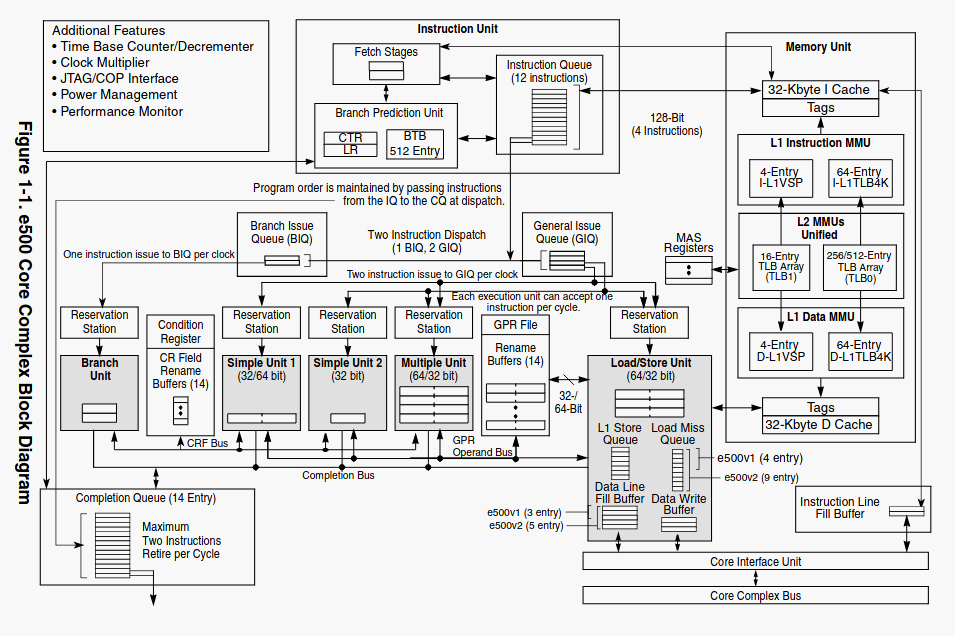

2.1 Schéma fonctionnel du processeur AMCC PowerPC 460EX

Le schéma du processeur 460EX est un peu déroutant au premier abord car il est assez détaillé. Alors, expliquons-le un peu. Tout d'abord, le FPU (Floating Point Unit - unité à virgule flottante) ne fait pas partie du coeur, comme c'est souvent le cas avec les processeurs PowerPC. Le FPU est connecté au processeur en tant qu'APU (Auxiliary Processor Unit - unité de processeur auxiliaire), il partage ses pipelines et dispose d'un ensemble standard de 32 registres FPR de 64 bits. Par conséquent, de notre point de vue, nous le considérerons comme faisant partie du coeur.

Ce processeur dispose de quatre bus internes :

- Processor Local Bus (PLB) : auquel sont connectées deux parties :

- La partie High Bandwidth (HB), qui relie les contrôleurs mémoire, PCIe et PCI, ainsi que le pont AHB.

- La partie à faible latence (LL), connecte la mémoire sur puce, deux contrôleurs DMA et le pont OPB.

- Bus périphérique sur puce (OPB) : connecte des périphériques plus lents ; le contrôleur de bus externe (EBC) est également connecté ici, auquel le coprocesseur Lattice XP2 de la Sam460 est relié.

- Advanced High-performance Bus (AHB) : connecte l'USB et, dans le cas de la Sam460ex, un contrôleur SATA II interne avec son propre contrôleur DMA.

- Bus Device Control Register (DCR) : connexion interne pour les informations d'état et de contrôle des composants individuels du processeur.

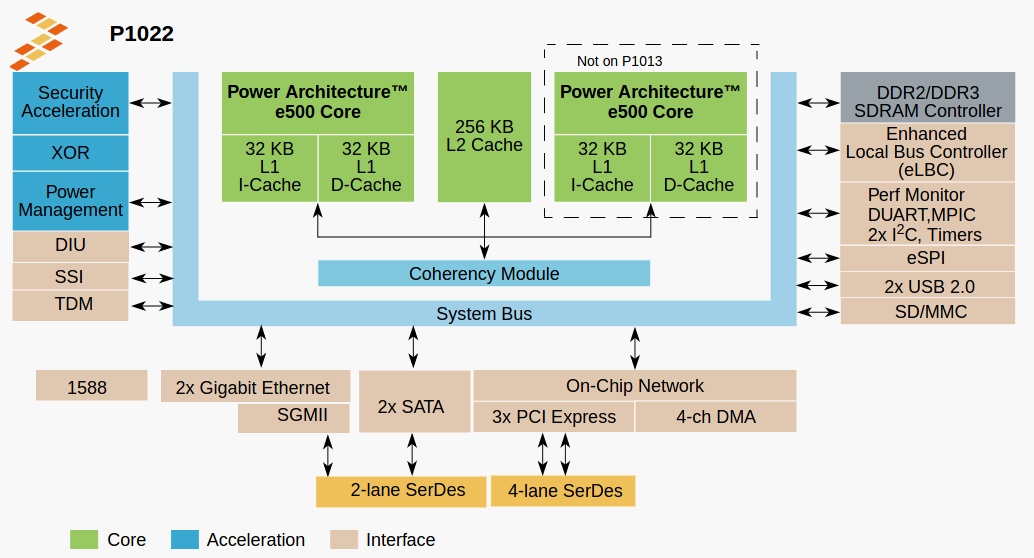

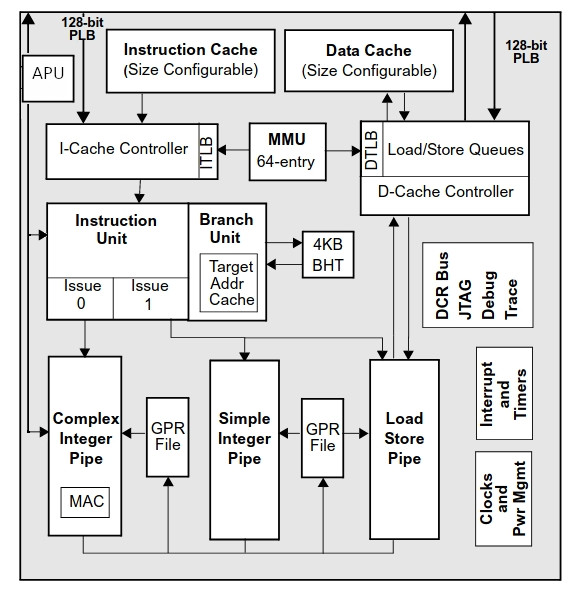

Ce schéma est moins détaillé, un bref résumé suffit donc. Les deux coeurs de processeur, ayant un cache L2 commun, sont connectés via le Coherency Module (module de cohérence) à la carte mère. Le coprocesseur Lattice LCMX02-640 est ensuite connecté via l'Enhanced Local Bus Controller (eLBC - contrôleur de bus local amélioré). Les autres connexions sont assez évidentes.

En plus des schémas, nous nous intéresserons principalement aux différences de caractéristiques des processeurs :

2.3 Informations de base sur les processeurs

| AMCC PowerPC 460EX | NXP QorIQ P1022 | |

| Description du processeur par le fabricant | Le processeur embarqué PowerPC 460EX est parfaitement adapté à une large gamme d'applications hautes performances, notamment l'imagerie, le contrôle industriel et la mise en réseau | La famille de processeurs P1022, une solution de produits Freescale économe en énergie, est conçue pour offrir des performances de traitement d'applications complexes avec une intégration de fonctionnalités exceptionnelle et une connectivité haut débit pour les réseaux IP et les applications avancées de traitement multimédia |

| Nombre de coeurs | 1 | 2 |

| Fréquence | 1,14 GHz | 1,2 GHz |

| MIPS (par coeur) | 2000 | 2880 |

| Type de coeur | PowerPC 440 | e500v2 |

Les deux processeurs ont un objectif similaire et, comme le suggère la description, ils possèdent tous deux de bonnes propriétés dans le domaine du réseau (Internet Protocol) et du traitement des flux de données (au moment de leur création).

La fréquence des processeurs est similaire, mais le P1022 propose des performances brutes par coeur nettement plus élevées à fréquence donnée, et il est également double coeur. Aujourd'hui, nous n'utilisons cette fonctionnalité que sous Linux, mais Hyperion travaille sur un nouvel ExecSG qui utilisera également les deux coeurs sous AmigaOS 4.

2.4 Sous-système mémoire des processeurs

| AMCC PowerPC 460EX | NXP QorIQ P1022 | |

| Cache L2 | 256 ko | |

| Cohérence de la mémoire | Sécurisé par surveillance du segment "Low Latency" du bus PLB ou par logiciel. La cohérence peut être perdue dans certaines circonstances | Sécurisé par le Coherency Module (ECM), qui surveille les transferts entre le bus, les coeurs e500v2 et le cache L2 |

| Mémoire sur puce | 64 ko | |

| Contrôleur de mémoire | DDR2-400 | DDR3-800 |

| Max. mémoire physique | 8 Go | 32 Go |

| Débit théorique | 3,2 Go/s | 6,4 Go/s |

| Nombre de rangs/banques physiques/signaux de sélection de puce | 4 | 4 |

| Entrelacement double canal/contrôleur | Non | Non |

| Entrelacement des rangs | Non | Oui |

| Contrôleur DMA | 1x monocanal haute vitesse 1x quatre canaux 1x pour SATA, non utilisé pour la Sam460LE |

2x universel à quatre canaux |

Les deux processeurs disposent d'un cache mémoire L2 de 256 ko. Avec le processeur 460EX, la cohérence mémoire n'est cependant pas garantie en toutes circonstances. Cela conduit, par exemple, à ce que les pilotes de périphériques doivent parfois vider le cache L2 et que les pilotes Radeon ne disposent pas d'un GART fonctionnel. Le P1022 sera donc légèrement plus rapide.

En plus de la mémoire L2, le processeur 460EX dispose également de 64 ko supplémentaires de mémoire rapide sur puce - elle est connectée par un bus de 128 bits et est utilisée, entre autres, pour les données par paquets traitées par le Security Engine (moteur de sécurité) et les modules Ethernet.

Le contrôleur DDR est une génération plus moderne dans le P1022. Il peut traiter plus de mémoire physique, il est plus rapide et même s'il ne dispose pas de double canal, il peut effectuer un entrelacement de rang, ce qui accélère les opérations d'environ 10%. Malheureusement, le micrologiciel de l'A1222+ ne peut pas encore initialiser cette fonctionnalité, mais comme U-Boot est encore en développement et que l'AmigaOne X5000 le permet déjà, nous pourrions disposer de cette fonctionnalité dans le futur.

Les deux ordinateurs n'ayant qu'un seul connecteur DDR sur la carte mère, nous sommes limités par la taille maximale des modules SO-DIMM. L'A1222 peut ainsi être équipé avec un module DDR3 jusqu'à 8 Go (à géométrie 2R ou 4R). J'ai essayé le module 8 Go (2R 8) Kingston Fury (KF318LS11IB/8). De son côté, la Sam460LE peut théoriquement disposer de 4 Go avec un module DDR2 (2R ou 4R). Je n'ai pas essayé cela, je n'ai pas de module 4 Go disponible. Il est annoncé un maximum de 2 Go de mémoire avec les Sam, mais comme U-Boot est également encore en développement, il serait possible d'ajouter la gestion de 4 Go de mémoire (si ce n'est pas déjà fait). Le processeur 460EX utilise un contrôleur DMA monocanal pour les transferts depuis des périphériques rapides (il peut faire des transferts mémoire<->mémoire et mémoire<->périphérique, pas directement périphérique<->périphérique) et le contrôleur à quatre canaux est destiné uniquement aux périphériques reliés à l'On-chip Peripheral Bus (bus périphérique sur puce). Le P1022 dispose de deux contrôleurs DMA universels à quatre canaux pour tous les transferts.

2.5 Contrôleurs de périphériques de processeur

| AMCC PowerPC 460EX | NXP QorIQ P1022 | |

| PCIe | 2x interface PCI Express v1.1 :

|

3x interface PCI Express v1.0a :

|

| PCI | 1x interface PCI v2.3, 32 bits/66 MHz | |

| SATA | 1x SATA II Rev. 2.5 (non connecté pour la Sam460LE) |

2x SATA II Rev. 2.0 |

| Ethernet | 2x 1 GbE (un seul connecté pour la Sam460LE) QoS, trames Jumbo Accélération TCP/IP :

|

2x 1 GbE QoS, trames Jumbo Accélération TCP/IP :

|

| Audio Vidéo | - | Interface LCD, 1280x1024P à 60 Hz, 24 bits |

| USB | 1x hôte USB 2.0 1x USB 2.0 OTG (non connecté pour la Sam460LE) |

2x USB 2.0 OTG (un seul connecté pour l'A1222+) |

| Moteur de sécurité | Sur puce en option | Sur puce en option |

| eSDHC | Contrôleur hôte numérique sécurisé amélioré, pour cartes SD/MMC (pour l'A1222+, utilisé pour U-Boot sur microSD) |

Le processeur P1022 dispose d'un total de six lignes configurables SERDES, une voie à quatre lignes, l'autre voie à deux lignes. La configuration est définie dans le micrologiciel.

La connexion physique de l'A1222+ propose 4x PCIe et 2x SATA. Si U-Boot le permet à l'avenir, une bifurcation peut être effectuée sur le port PCIe (divisant le bus PCIe sans commutateur). Le processeur peut avoir jusqu'à trois interfaces PCIe, les véritables combinaisons utilisables sont donc : PCIe x4 (par défaut), PCIe x2 + x2, PCIe x2 + x1 + x1. De cette manière, il serait possible à l'avenir, d'étendre l'A1222+ avec des périphériques supplémentaires, bien sûr au prix d'une limitation du flux de données vers la carte graphique.

Le processeur 460EX partage un SERDES (marqué comme "HSS" sur le schéma du PowerPC 460EX) pour PCIe x1 et SATA. Sur la Sam460LE, le PCIe x1 est câblé.

Les deux processeurs disposent d'une accélération matérielle pour le TCP, l'e500v2 dispose également des fonctions de VLAN avancées, de QiQ, de MPLS, etc. Bien sûr, ces fonctions sont inutilisées dans la pile TCP AmigaOS (jusqu'à présent).

Les deux processeurs peuvent également disposer d'un moteur de sécurité (SEC), apportant l'accélération matérielle IPSEC, SSL/TLS et de nombreux autres algorithmes de cryptographie et de hachage. Mais cette option est facultative lors de la commande du processeur, donc je suppose que ni la Sam460LE ni l'A1222+ n'ont de versions SEC de leur processeur (et je ne veux pas enlever les ventilateurs juste pour regarder le code). Comme c'est déjà le cas avec les gros processeurs, il serait possible d'échanger les processeurs contre des versions avec ce moteur. Et puis (euh...), il faudra écrire un pilote pour AmigaOS (Linux peut-il gérer cela ?). L'avantage serait ainsi, par exemple, une accélération significative du trafic Internet. Et ceci ne ferait certainement pas de mal de nos jours, où tout est crypté.

Une comparaison des processeurs montre que le P1022 a finalement un peu plus d'avantages. Mais nous n'avons pas encore découvert l'essentiel.

Dans le prochain chapitre, nous irons encore plus loin, dans les entrailles du processeur,

jusqu'au coeur. Voyons si nous pouvons également y trouver quelque chose d'agréable

3.1 Différences dans les coeurs

| PowerPC 440 | e500v2 | |

| ISA | Power ISA v.2.03 - BookIII-E | Power ISA v.2.03 - BookIII-E |

| Architecture | 32 bits | 32 bits |

| Cache L1 | 32 ko de cache I, 32 ko de cache D | 32 ko de cache I, 32 ko de cache D |

| Espace d'adressage virtuel | 41 bits (2 To) | 41 bits (2 To) |

| Espace d'adressage physique | 36 bits (64 Go) | 36 bits (64 Go) |

| Principaux registres | 32x 32 bits à usage général (GPR) 32x 64 bits à virgule flottante (FPR) Il s'agit de la norme PowerPC |

32x 64 bits à usage général (GPR) Les 32 bits supérieurs des registres sont utilisés uniquement par les instructions SPE, à virgule flottante double précision et à virgule flottante vectorielle (voir ci-dessous) |

| FPU PowerPC | Oui, connecté au coeur 440 en tant qu'APU (Auxiliary Processor Unit) 2 MFlops/MHz |

Il ne dispose pas d'unité standard, le FPU est remplacé par les unités Embedded FPU ci-dessous |

| Extension du jeu d'instructions PowerPC standard | DSP (Digital Signal Processing), instructions rapides à cycle unique : 32 bits x 32 bits -> 32 bits 16 bits x 16 bits -> 32 bits 16 bits x 16 bits + 32 bits -> 32 bits, c'est-à-dire multiplication d'entiers et multiplication avec addition (MAC = multiple-accumulate) | SPE (Signal Processing Engine), SIMD utilise des vecteurs 64 bits avec deux valeurs d'entier de 32 bits. Il contient également les instructions DSP dont dispose le coeur du PowerPC 440 |

| Unité FPU scalaire simple précision à virgule flottante intégrée (SSPFP), simple précision, mais sans instructions FPU PowerPC standard | ||

| Vecteur intégré à virgule flottante simple précision (VSPFP), identique mais SIMD, vecteur 64 bits avec deux composants à virgule flottante 32 bits | ||

| Unité FPU scalaire double précision intégrée à virgule flottante (SDPFP), double précision et, encore une fois, sans instructions PowerPC FPU standard | ||

| Instruction de Sélection d'entier (isel) qui élimine les segments de sauts conditionnels dans les calculs SIMD | ||

| Détermination de l'instruction rapide de "recherche de chaîne" de zéro octet la plus à gauche (dlmzb) |

Les deux coeurs sont 32 bits et ont le même ISA. Ils diffèrent par les jeux de registres, les unités FPU et les unités SIMD.

Jetons à présent un coup d'oeil aux diagrammes de base. Cette fois, le schéma de l'e500v2 sera plus détaillé.

3.2 Schéma fonctionnel du PowerPC 440

Coeur du PowerPC 440. Le bloc FPU n'est pas sur le schéma, il est connecté à l'interface APU

Le FPU, même s'il n'est pas directement dans le coeur, se comporte comme une partie de celui-ci. Il est connecté à l'interface APU et partage directement les pipelines centraux (Complex Integer Pipe).

Il n'y a que des registres GPR 32 bits dans le coeur. Les registres FPR 64 bits sont à nouveau contenus dans le FPU externe et, du point de vue de l'ABI (Application Binary Interface), ils apparaissent comme faisant partie du coeur.

Cependant, ce qui est en plus dans le coeur par rapport aux processeurs PowerPC classiques, c'est l'extension DSP/MAC (APU). Elle est contenue directement dans le Complex Integer Pipe. Le temps d'exécution de ces instructions est d'un cycle, elles sont donc adaptées au traitement de flux de données similaires (flux).

3.3 Schéma fonctionnel de l'e500v2

Ce coeur comporte cinq puissantes unités (les grises sur le schéma), traite les instructions dans le désordre (jusqu'à deux instructions + un saut par cycle) et les termine dans l'ordre. Ce coeur ne dispose également que de registres GPR, mais cette fois étendus à 64 bits. FPR ne contient aucun registre.

Le FPU PowerPC standard n'est pas présent, il est remplacé par les unités suivantes : Flottant scalaire intégré à simple précision et Flottant scalaire intégré à double précision. Ces unités ont cependant un jeu d'instructions différent de celui du FPU PowerPC et utilisent un GPR 64 bits directement au lieu du FPR.

Les unités SIMD (Simple Instruction Multiple Data) sont les plus intéressantes sur ce processeur. Il en contient deux : SPE (Signal Processing Engine) est une unité vectorielle qui traite des vecteurs entiers avec deux valeurs de 32 bits ou quatre valeurs de 16 bits. L'APU à virgule flottante simple précision vectorielle intégré est une unité vectorielle pour les vecteurs avec deux valeurs à virgule flottante. Les instructions SPE sont exécutées directement en unités simples et multiples de 64 bits (Unit) et utilisent à nouveau le GPR 64 bits. A titre de comparaison, Altivec/VMX gère des vecteurs deux fois plus longs (128 bits) et dispose d'une unité de permutation supplémentaire. Ici, dans les coeurs, se trouve enfin la réponse à toutes les questions quant à savoir si l'A1222+ (ou son processeur) est suffisamment puissant ou adapté à AmigaOS.

4. La réponse à la question fondamentale de la vie, de l'univers et des Amiga NG d'entrée de gamme en général

La question fondamentale est la suivante : l'A1222+ est-il plus puissant que la Sam460LE ? Contrairement aux souris, nous n'avons pas besoin d'attendre sept millions d'années pour obtenir une réponse. La réponse n'est pas 42, mais elle est quand même très simple : oui et non.

Non : parce que le code PowerPC normal contenant les instructions FPU doit être traité via des interruptions et émulé pour le processeur P1022. Nous avons deux émulateurs d'instructions FPU disponibles sur AmigaOS :

- LTE (émulateur à temps de chargement) : c'est la valeur par défaut. Il s'agit d'un traducteur JIT avec une vitesse relativement élevée. Lors de mes tests, il n'était que 1,2 à 4,5 fois plus lent que le FPU d'origine. C'est correct. Il présente cependant un inconvénient : comme tout compilateur JIT, il n'a pas une compatibilité à 100% avec le code original. Certaines applications ne fonctionnent pas avec.

- Émulateur interprétatif normal : nous l'utiliserons si le LTE ne fonctionne pas (défini dans Prefs:Compatibility). Il est nettement plus lent (20x à 70x) que le FPU classique, mais il est 100% compatible. C'est en fait la même chose qu'avec le MC68LC060 et la softieee.library sur Amiga Classic. Ce n'est pas rapide, mais ça marche. Et c'est la raison pour laquelle des applications comme Blender ou certains jeux d'action 3D seront lents sur l'A1222+, jusqu'à ce que quelqu'un les compile nativement pour l'A1222+.

Oui (et largement) : parce que l'e500v2 intègre également deux extensions SIMD. Elles ne sont pas aussi puissantes que l'AltiVec/VMX susmentionné, qui surpassait d'ailleurs complètement les SSE et SSE2 d'Intel à l'époque, mais ils restent intéressants. L'instruction "Integer Select", qui supprime les sauts conditionnels dans le code SIMD, sert de complément aux calculs vectoriels. Voir par exemple dans cet article (paragraphe 2.5). Si nous avons du code d'application écrit directement pour le traitement SIMD, il sera nettement plus rapide que le code PowerPC classique.

Du point de vue du développeur, l'utilisation du FPU embarqué (Embedded FPU) et du SPE est encore plus compliquée. eFPU a un ensemble de registres différent de celui du standard PowerPC, donc appeler des fonctions à virgule flottante à partir de bibliothèques standard comporte certaines difficultés. Et je ne parle pas du fait que les instructions SPE nécessitent un alignement de pile sur 8 octets. Cela devrait aller de soi selon la norme ABI PowerPC, mais toutes les applications ne la suivent pas. Pour plus de détails, lisez cet article.

La Sam peut faire plus : toutes les Sam460 et Sam440 sont capables d'exécuter des instructions DSP (MAC) rapides à un seul cycle (voir ci-dessus). Oui, toutes, car leurs processeurs ont le même coeur : le PPC440. Si nous avions une tâche chronophage dépendante de multiplications et d'additions d'entiers (par exemple, la plupart des opérations de cryptographie et de hachage ainsi que certains codecs), les Sam4x0 peuvent également être plus rapides que le code PowerPC classique. Le SPE dans le P1022 ou l'Altivec dans les PowerPC G4 disposent également de telles instructions, mais le processeur PowerPC G3, par exemple, ne peut pas le faire. Il ne peut donc pas le faire aussi vite.

De plus, l'utilisation d'instructions DSP dans les Sam4x0 présente un gros avantage : elle utilise une ABI standard, il n'est donc pas nécessaire d'apporter des modifications à d'autres codes comme dans le SPE. Donc, en général, je plaiderais auprès des développeurs pour qu'ils utilisent cette option pour les ordinateurs Sam4x0.

Les Sam4x0 contiennent également l'instruction "dlm from b". Elle est utilisée pour une recherche rapide dans la chaîne, exactement comme son nom l'indique : elle recherche le premier octet non nul. Cependant, je n'ai aucune idée des tâches pour lesquelles elle pourrait être utilisée dans un système d'exploitation de bureau.

5. La fin et la suite

Nous savons maintenant quels sont les avantages des ordinateurs et de leurs processeurs. Leurs prédécesseurs des premières générations ne pouvaient pas utiliser des cartes PCIe modernes et des contrôleurs plus récents. Bien sûr, ils n'atteignent pas les performances de leurs grandes soeurs AmigaOne X1000 et X5000, ce sont après tout des systèmes d'entrée de gamme.

Mais les deux ont quelque chose en plus par rapport aux processeurs de bureau PowerPC G3. Ils peuvent utiliser les instructions "Multiply-accumulate" (MAC) et l'A1222+ dispose également de deux unités SIMD. C'est dommage que ces options restent inutilisées, il vaudrait certainement la peine de recompiler certains algorithmes chronophages en prenant en compte les avantages du SPE et du MAC.

La prochaine fois, nous pourrons donc commencer à tester du matériel réel.

Cela ira vite, je possède quatre assistants similaires à celui-ci qui sont

déjà très expérimentés dans le domaine de l'informatique.

Crédits

- ACube et AAA Technology pour ces nouveaux beaux jouets.

- Logos : shop.acube-systems.biz, a1222plus.com, modifié.

- Cartes mères : shop.acube-systems.biz, amigakit.fr, modifié.

- Iceberg : flickr.com.

- Deep Sea Octopus : g.cz.

- Schémas des processeurs : fiche technique du processeur intégré PowerPC 460EX et spécifications matérielles du processeur intégré QorIQ P1022.

- schéma modifié : manuel d'utilisation du coeur du processeur PPC440x5 et manuel de référence de la famille PowerPC coeur e500, modifié.

- Chat : the-great-beyond.blogspot. com.

|

|