|

Jeudi 02 octobre 2025 - 09:22 |

| Translate |

|

| Rubriques |

| Réseaux sociaux |

|

| Liste des jeux Amiga |

|

| Trucs et astuces |

|

| Glossaire |

|

| Galeries |

|

| Téléchargement |

|

| Liens |

|

| Partenaires |

|

| A Propos |

|

| Contact |

|

|

|

Cet article a été initialement publié sur amigaportal.cz en novembre 2022. L'article est une suite libre des deux parties précédentes sur l'AmigaOne XE :

Nous allons aborder les interruptions matérielles de cet AmigaOne. Il y aura plus de théorie et de technique ici. Comme je ne comprenais pas vraiment le système d'interruptions PCI de l'AmigaOne XE, j'ai dû le chercher, et vous pouvez le trouver ici également. Et je dois dire que c'est beaucoup plus compliqué que le système PCIe actuel.

Cet article se présente donc comme un petit manuel destiné aux utilisateurs débutants et intermédiaires sur le thème des interruptions PCI. Or, les manuels ont tendance à être ennuyeux, alors préparez-vous à cela.

1. Pourquoi faisons-nous tout cela ?

Je souhaite absolument en savoir un peu plus sur mon AmigaOne XE (et pas seulement sur celui-ci, les interruptions seront très similaires pour tous les Amiga NG de première génération, AmigaOne SE, Micro A1-C, Pegasos 1 et Pegasos 2).

Et aussi parce que certaines choses ne fonctionnent pas dans notre AmigaOne XE et que le dernier micrologiciel officiel U-Boot 1.1.1 ne peut pas initialiser correctement les cartes PCI derrière le pont.

J'aimerais essayer d'activer les interruptions pour les cartes PCIe derrière le pont PCI-PCIe. Ce n'est pas grand-chose, hein ?

2. Documentation

Comme je n'ai pas très bien compris ce problème, j'ai dû lire de la documentation cette fois-ci, ce que je n'aime vraiment pas faire. Pour quiconque souhaitant vérifier mes procédures et considérations, je recommande cette littérature :

- PCI localbus specification rev. 2.2 (Spécification du bus local PCI rév. 2.2) - nous savons que l'arbitre du bus PCI est le northbridge Articia S. Je n'ai pas trouvé le manuel de l'Articia S (uniquement la fiche technique), mais je suppose qu'il est compatible PCI rev. 2.2. Heureusement, il n'y a pas de problème majeur : la version 2.1 de l'Articia est compatible (la version 2.1 a introduit la fréquence de 66 MHz, ce que l'Articia peut faire), la version 2.2 l'est probablement (il s'agit d'une modification mineure de la v2.1) et la version 2.3 de l'Articia S n'est plus compatible (la v2.2 a désactivé les cartes PCI 5 V). De plus, le southbridge de l'AmigaOne XE est compatible PCI v2.2, nous considérerons donc la v2.2 comme valide.

- PCI-to-PCI Bridge Architecture Specification rev.1.1 (Spécification d'architecture de pont PCI vers PCI rev.1.1) - Il s'agit de la version qui était valable au moment de la norme PCI v2.2.

- PCI Express-to-PCI/PCI-X Bridge Specification rev.1.0 (Spécification du pont PCI Express vers PCI/PCI-X rev.1.0) - Cette version est compatible avec nos deux ponts PCI vers PCIe testés.

- PLX Technology: PEX 8112-AA PCI Express-to-PCI Bridge Data Book (PLX Technology : Manuel de données sur le pont PCI Express vers PCI PEX 8112-AA).

- Pericom: PI7C9X111SL PCI Express-to-PCI Reversible Bridge Datasheet (Pericom : Fiche technique du pont réversible PCI Express vers PCI PI7C9X111SL).

3. Bus PCI dans AmigaOne XE plus en détail

Cette fois, nous allons nous intéresser uniquement au PCI du northbridge Articia S, mais de manière plus détaillée.

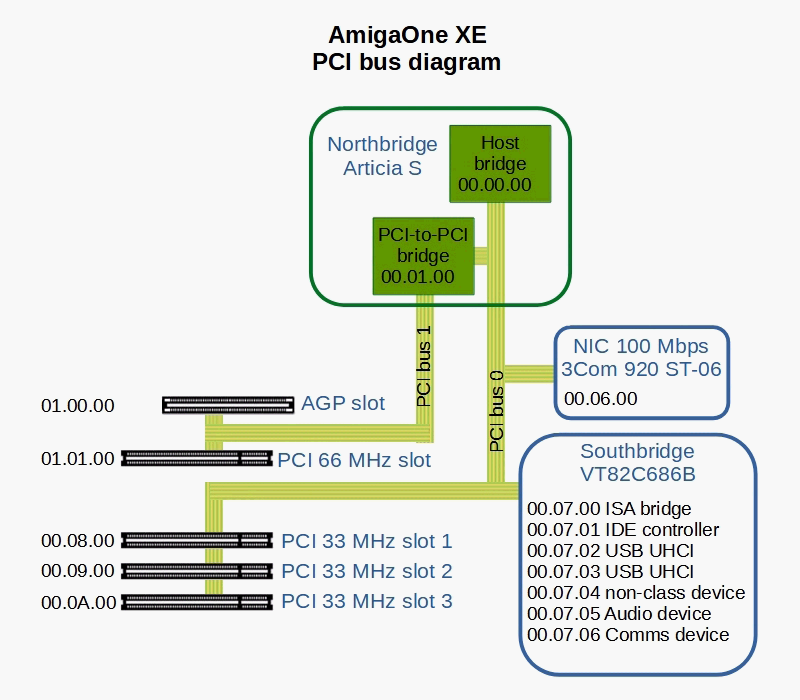

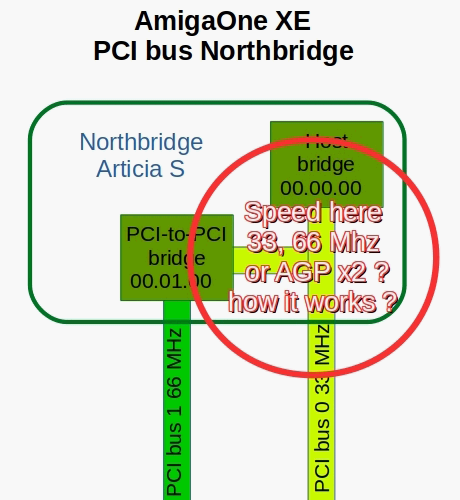

Schéma 3.1 - Bus PCI de l'AmigaOne XE

- XX = numéro de bus (bus nr.)

- YY = numéro de périphérique sur le bus (device nr.). Le périphérique est par exemple une carte PCI.

- ZZ = fonction du périphérique (function nr.), généralement le périphérique a une fonction (.00), mais il peut en avoir plusieurs.

- 00.00.00 = pont hôte. Il s'agit d'une sorte de concentrateur racine dans les cartes PCIe modernes. Point de départ du contrôleur (arbitre PCI).

- 00.01.00 = pont PCI vers PCI. Vous pouvez constater que le bus PCI 1 (AGP+PCI 66) ne possède pas de pont hôte (concentrateur racine dans la terminologie PCIe actuelle), mais est connecté au bus PCI 0 via un pont PCI vers PCI. Ce pont est donc le premier périphérique (00.01.00) après le pont hôte sur le bus PCI 0. Le bus PCI 1 démarre derrière ce pont.

Autrement dit, derrière deux ponts. Et la carte derrière deux ponts ne peut plus être initialisée par U-Boot.

- 00.06.00 - Ethernet sur la carte mère.

- 00.07.00 - southbridge VT82C686B. Vous pouvez constater que le southbridge est un périphérique PCI unique (.07.), mais qu'il possède de multiples fonctions. En fait, vous y trouverez la plupart des périphériques internes de l'AmigaOne XE : IDE, USB 1.1, audio, série.

- 00.08.00 - il s'agit de l'adresse du périphérique (carte) dans le port PCI 33 MHz numéro 1.

- 00.09.00 - il s'agit de l'adresse du périphérique (carte) dans le port PCI 33 MHz numéro 2.

- 00.0A.00 - il s'agit de l'adresse du périphérique (carte) dans le port PCI 33 MHz numéro 3.

- 01.00.00 - il s'agit de l'adresse du périphérique (carte) dans le port AGP. Notez qu'il est déjà connecté à un autre bus PCI (01.xx.xx = bus PCI 1).

- 01.01.00 - il s'agit de l'adresse du périphérique (carte) dans le port PCI 66 MHz.

Essayez de voir si vous ne trouvez pas quelque chose d'étrange dans ce schéma. Vous découvrirez la solution à la fin de l'article.

4. À quoi ressemble le système d'interruptions PCI dans l'AmigaOne XE

Dans l'AmigaOne XE, la fonction de contrôleur d'interruptions PCI est assurée par le southbridge VT82C686B. Si vous souhaitez rechercher quelque chose, il s'agit du premier système d'interruptions PCI, désormais appelé "PCI ancien", et non de la version plus récente PCI MSI (Message Signalled Interrupts).

L'affectation des lignes d'interruption est gérée par le micrologiciel. Dans notre cas, il s'agit d'U-Boot. Nous disposons de la dernière version officielle d'Hyperion : U-Boot 1.1.1.

4.1 Affectation de base des broches INTx# pour les périphériques PCI

Chaque périphérique PCI peut utiliser jusqu'à quatre interruptions matérielles différentes pour signaler une interruption. Quatre broches physiques, INTA#, INTB#, INTC# et INTD#, leur sont réservées sur le connecteur PCI (pour information, sur le connecteur PCI, ce sont les broches A6, A7, B7, B8).

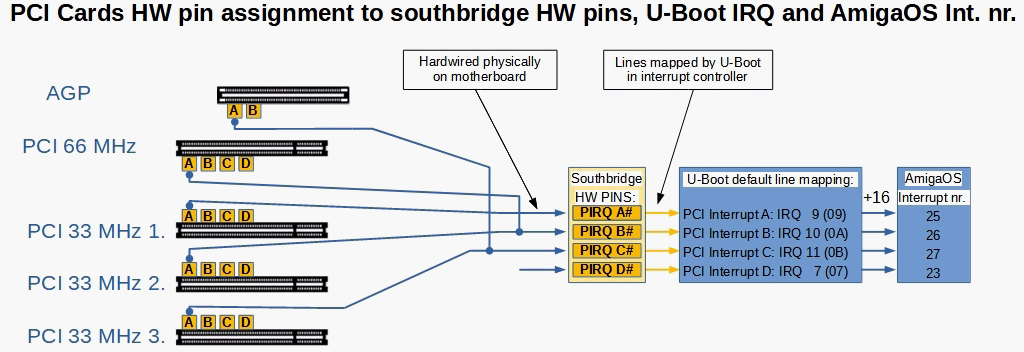

Le périphérique AGP ne possède que deux broches matérielles INTA#, INTB# (A6, B6). Il est important de noter que ces signaux sont physiquement connectés au contrôleur d'interruption (définition : IRQ Pin = une indication de la broche physique de la carte PCI utilisée par la fonction). Les câbles de données du bus PCI sont connectés au pont nord, comme illustré sur le schéma 3.1. Cependant, les broches d'interruption sont reliées au contrôleur d'interruptions, le pont sud, où elles sont connectées aux broches du contrôleur d'interruption physique, comme suit :

- Les carrés A, B, C, D sont les broches d'interruptions physiques INTA#, INTB#, INTC# et INTD# sur les cartes PCI.

- PIRQ A#, PIRQ B#, PIRQ C#, PIRQ D# sont les broches physiques du contrôleur d'interruptions, le southbridge (le nôtre n'a que quatre broches, généralement il peut y en avoir plus).

- La PIRQ A# est connectée à un périphérique dans le port PCI 33 MHz numéro 1.

- Les périphériques dans le port PCI 66 MHz et le port PCI 33 MHz numéro 2 sont connectés à la PIRQ B#.

- Les périphériques dans le port AGP et le port PCI 33 MHz numéro 3 sont connectés à la PIRQ C#.

- Il n'y a rien de connecté à la PIRQ D# dans ce diagramme.

Dans l'ancienne architecture ISA, chaque périphérique devait avoir un numéro d'interruption unique. Je ne sais pas si vous vous en souvenez, mais avec le très ancien PC XT/AT, lors de l'utilisation de plusieurs cartes, il était souvent nécessaire de définir manuellement les numéros d'interruption afin d'éviter tout conflit.

Cependant, dans l'architecture PCI, les interruptions matérielles physiques peuvent déjà être partagées et les conflits sont résolus par leur priorité différente. Le contrôleur d'interruption de l'AmigaOne XE est de type APIC (Advanced Programmable Interrupt Controller), il contient un routeur d'interruption et avec lui U-Boot affecte les interruptions matérielles individuelles aux IRQ, c'est-à-dire attribue des lignes. (Définition : ligne d'interruption = configuration, détermine quel numéro d'IRQ est attribué à chaque fonction PCI)

Dans le diagramme 4.1, vous pouvez voir comment les lignes sont attribuées dans l'AmigaOne XE (si vous laissez les paramètres par défaut dans le menu U-Boot "PCI/AGP") :

- La PIRQ matérielle A# (marquée comme interruption PCI A dans U-Boot) est affectée sur l'IRQ 9 (0x09).

- La PIRQ matérielle B# (marquée comme interruption PCI B dans U-Boot) est affectée sur l'IRQ 10 (0x0A).

- La PIRQ matérielle C# (marquée comme interruption PCI C dans U-Boot) est affectée sur l'IRQ 11 (0x0B).

- La PIRQ matérielle D# (marquée comme interruption PCI D dans U-Boot) est affectée sur l'IRQ 7 (0x07).

Je suppose que cela est basé sur le modèle ISA précédent où les seize premières interruptions étaient réservées aux interruptions ISA.

(Définition : numéro d'interruption = numéro d'interruption de la fonction PCI dans le système d'exploitation)

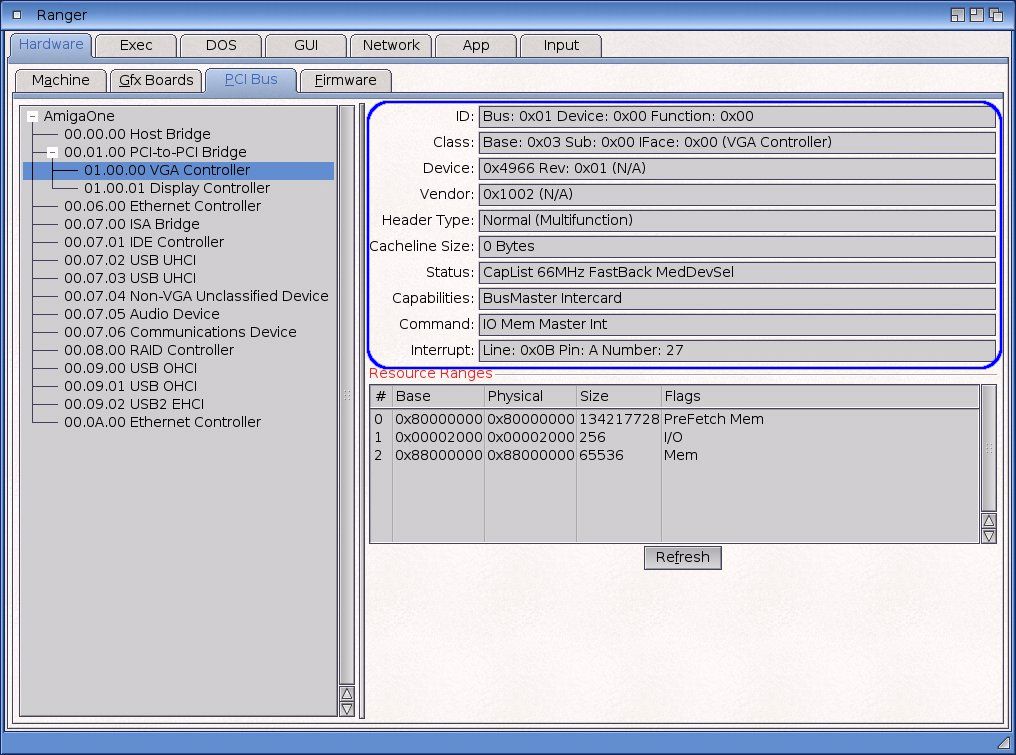

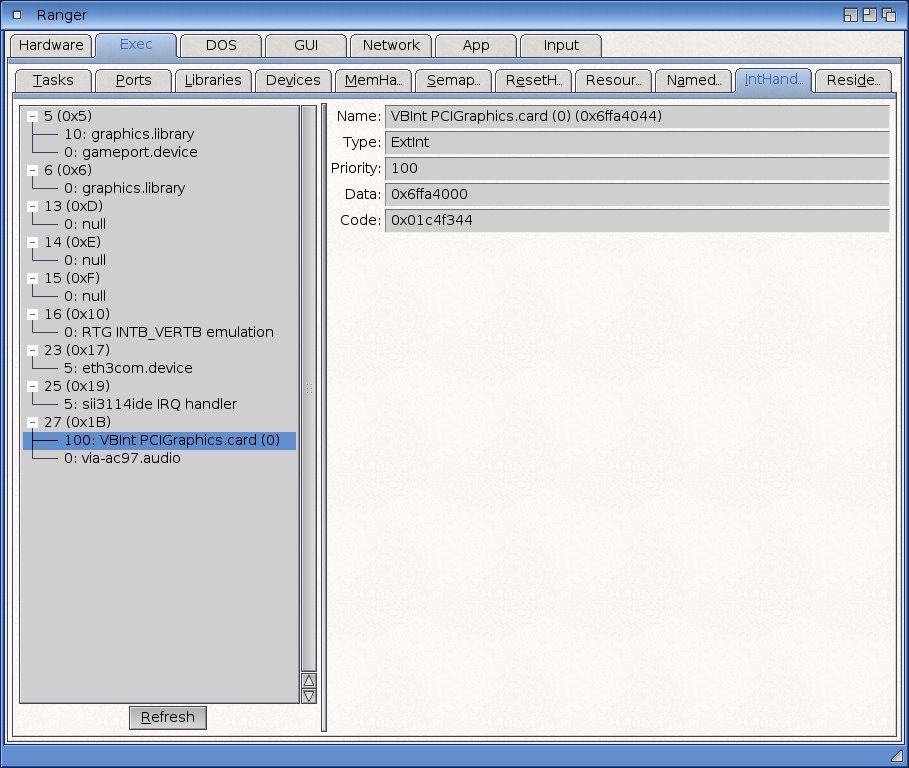

4.2 Petit exercice dans Ranger

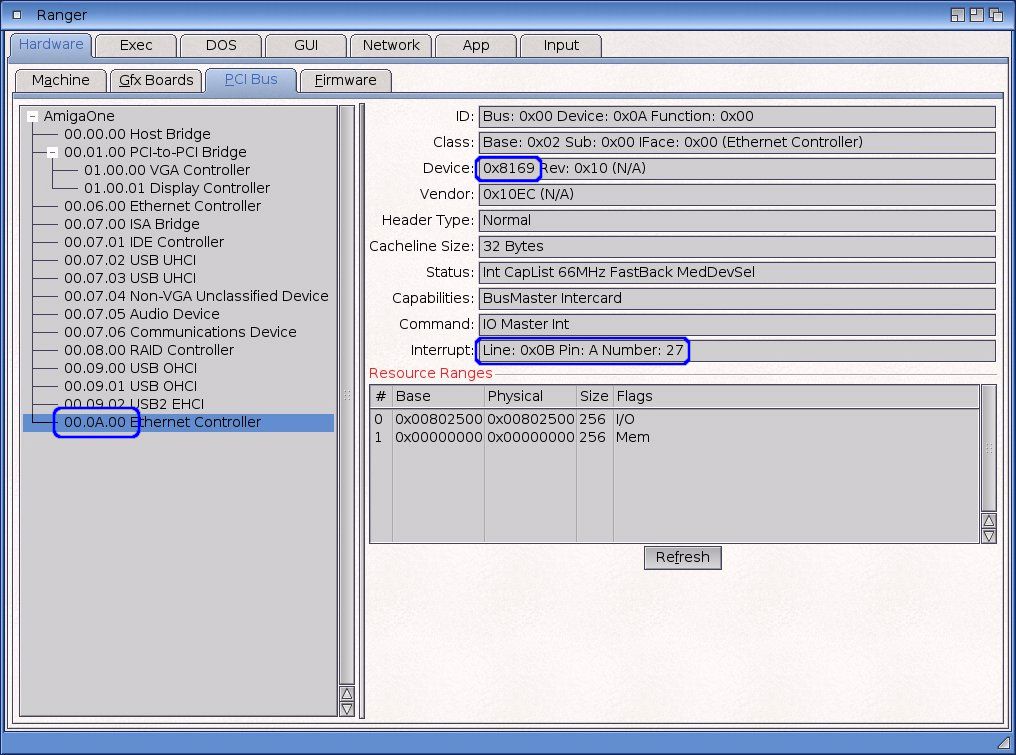

La figure 4.2 montre les résultats du programme Ranger. Voici ce que nous voyons :

- La carte Ethernet a l'adresse 00.0A.00, c'est-à-dire qu'elle est branchée sur le port PCI 33 MHz numéro 3.

- C'est le type RTL8169.

- A la ligne d'interruption 0x0B (= 11) attribuée, l'interruption matérielle est sur la broche A de la carte PCI et le numéro d'interruption dans AmigaOS est 27 (11+16=27).

- rtl8169.device a le numéro d'interruption 27 (0x1B).

- La priorité d'interruption de ce périphérique est 5.

- L'interruption 27 est partagée avec trois autres périphériques et la priorité 100 (la plus élevée) a la carte graphique.

Mais que se passe-t-il si la carte PCI possède davantage de fonctions et encore plus d'interruptions ? C'est le cas du southbridge du schéma 3.1. Mais ce n'est pas tout : certaines cartes courantes ont plusieurs fonctions. Elles peuvent nécessiter davantage d'interruptions physiques.

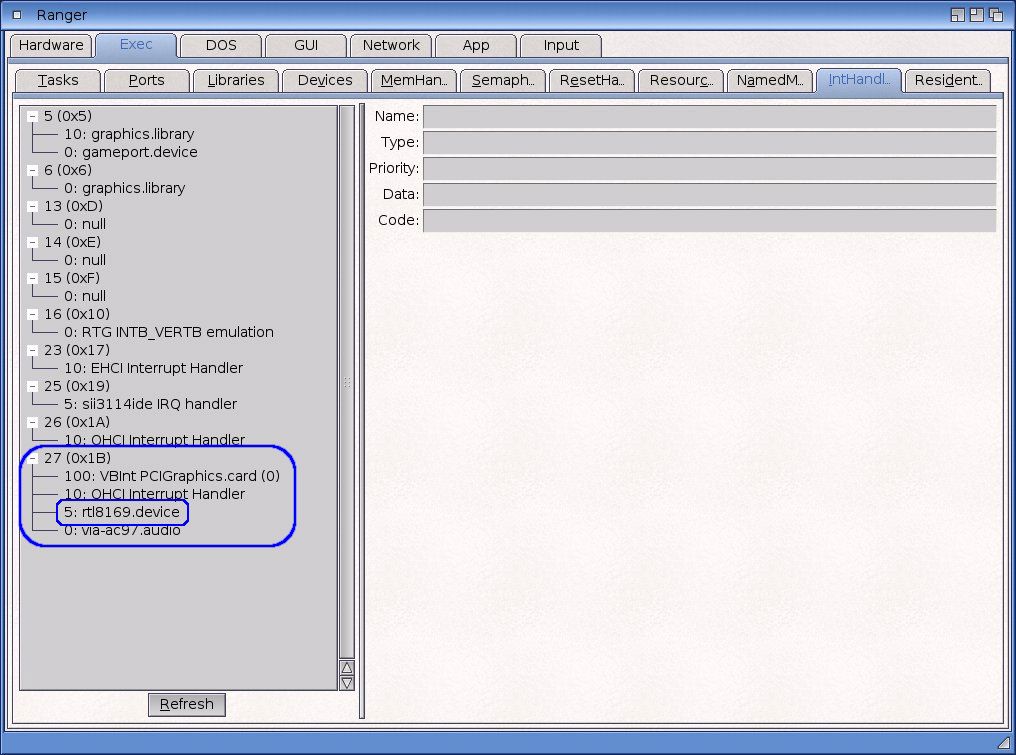

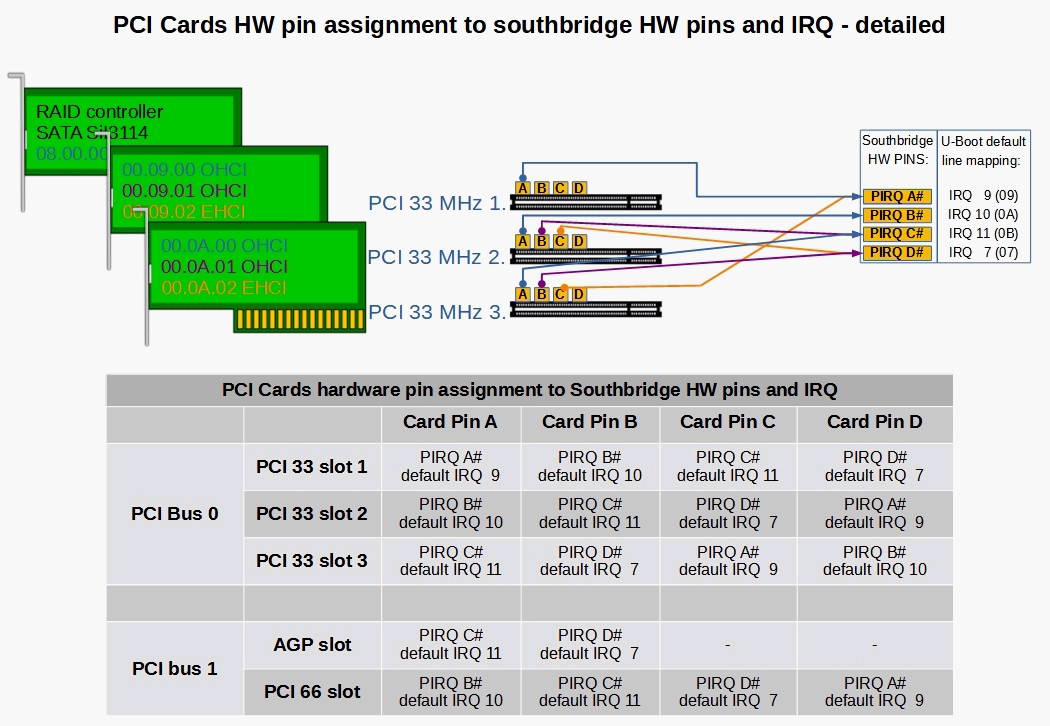

C'est là que les choses se compliquent. Le schéma 4.4 montre trois cartes PCI :

- Contrôleur SATA dans le port PCI 33 MHz numéro 1 : il ne possède qu'une seule fonction et une seule interruption matérielle (broche A = INTA#). Il est physiquement connecté à la PIRQ A# du contrôleur.

- Carte USB 2.0 dans le port PCI 33 MHz numéro 2 : elle possède trois fonctions et chacune d'elles

possède sa propre interruption matérielle.

- 00.09.00 : l'USB OHCI est connecté à la broche A de la carte PCI et physiquement connecté à la PIRQ B# du contrôleur.

- 00.09.01 : l'USB OHCI est connecté à la broche B de la carte PCI et physiquement connecté à la PIRQ C# du contrôleur.

- 00.09.02 : l'USB EHCI est connecté à la broche C de la carte PCI et physiquement connecté à la PIRQ D# du contrôleur.

- La broche D de cette carte reste inutilisée.

- Vous pouvez voir que chaque fonction avec sa propre interruption est connectée à une broche physique différente de la carte et du contrôleur, simplement en décalant une position à chaque fois.

- Carte USB 2.0 dans le port PCI 33 MHz numéro 3 : il s'agit de la deuxième carte USB à l'adresse PCI de 00.0A.00 à 00.0A.02 et on voit que les connexions matérielles sont à nouveau décalées d'une unité.

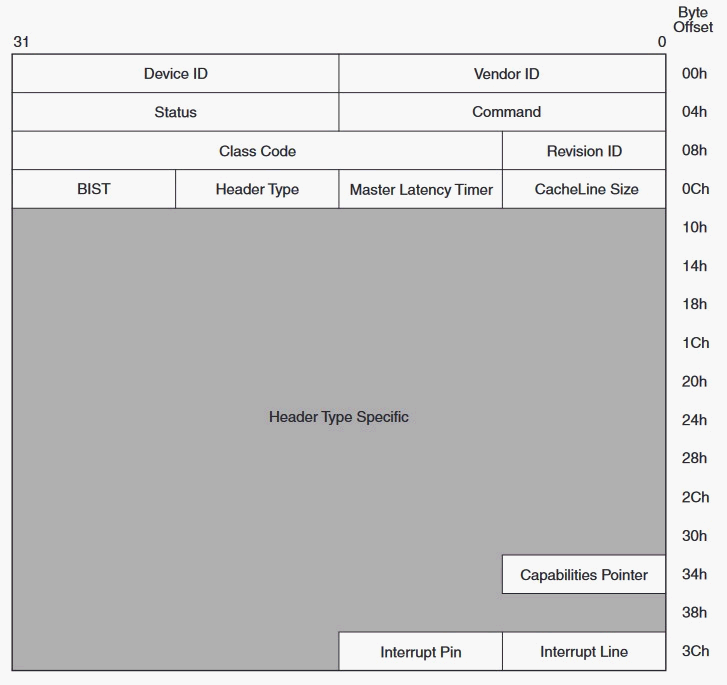

4.4 En-tête PCI

Chaque fonction PCI possède son propre espace de configuration en mémoire. Celui de base est appelé "PCI header" (en-tête PCI). Il existe plusieurs types d'en-têtes. Le type 00h est l'en-tête des fonctions PCI standard et le type 01h est l'en-tête de pont.

Les périphériques PCIe ont généralement un en-tête légèrement différent, mais le bus PCI voit uniquement l'en-tête 00h de la carte PCIe et uniquement l'en-tête 01h du pont PCI-PCIe. Dans ce cas précis, PCI et PCIe sont donc identiques.

Figure 4.5 - en-tête PCI

Notez que Ranger affiche simplement les données d'en-tête PCI.

5. Exploration de la carte graphique PCIe derrière le pont PCI-PCIe

Nous connaissons donc maintenant un peu la théorie. Examinons à présent de plus près ce qui se passe dans notre AmigaOne XE lors de l'initialisation d'un périphérique PCI. Nous savons déjà que notre carte graphique derrière le pont PCI-PCIe n'est pas correctement initialisée. Mais à quoi ressemble une initialisation aussi correcte ? Pour cela, il vous faudrait lire les spécifications plus en détail que moi et probablement avoir une connaissance plus approfondie d'AmigaOS. Utilisons donc une petite méthode comparative.

J'ai pris le pont PCI-PCIe et la carte graphique HD7750 et je les ai d'abord connectés sur l'AmigaOne XE puis sur la Sam440ep-flex. Cela devrait être plus ou moins équivalent à l'utilisation de ponts et de cartes. Et nous savons que dans la Sam440ep-flex, cela fonctionne comme prévu.

Les valeurs varieront certainement dans les adresses des périphériques PCI, les affectations de lignes et les numéros d'interruption - tout dépend de la conception spécifique de l'ordinateur, mais d'autres caractéristiques "devraient être les mêmes". Pour le Sam440ep-flex, l'arbitre du bus PCI est le processeur AMCC440 lui-même. Le PCI est ici conforme à la norme v2.2. Cependant, je pense que les fonctions MSI avancées ne sont pas utilisées sous AmigaOS ; il suffit de regarder les numéros d'interruption affectés : là encore, ils sont tous décalés de 16, et il n'y a rien de plus sophistiqué.

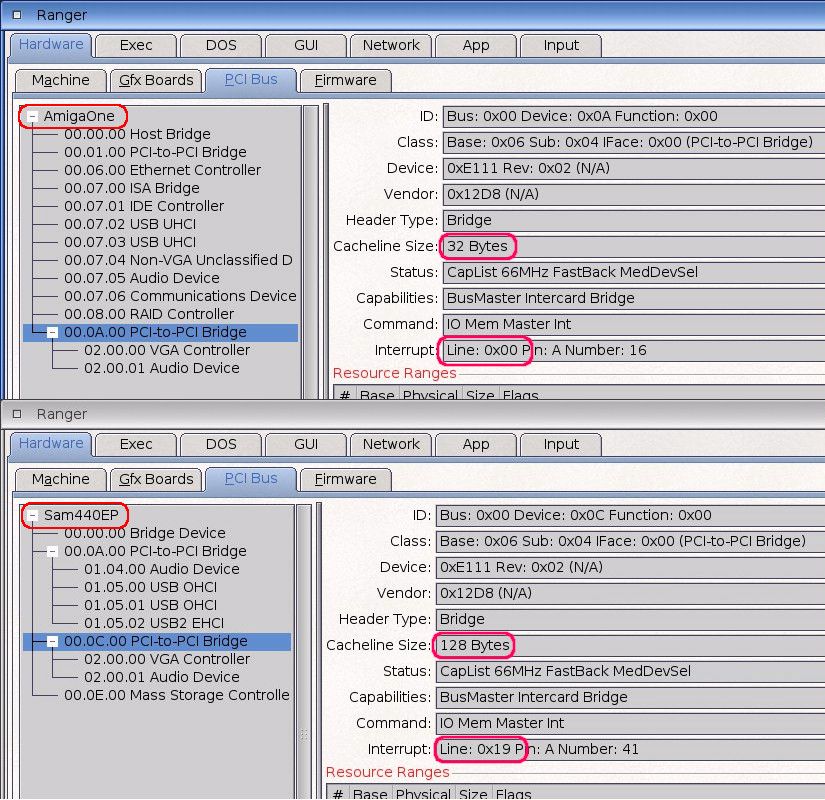

5.1 Comparaison des ponts AmigaOne XE et Sam440ep-flex

Commençons par examiner comment les ponts sont initialisés. En comparant le même pont PCI-PCIe sur AmigaOne XE et Sam440ep-flex, nous constatons les valeurs "0x00" pour la ligne d'interruption de l'AmigaOne XE et "0x19" pour la Sam440ep-flex.

Figure 5.1 - comparaison du pont pour l'AmigaOne XE et la Sam440ep-flex

L'AmigaOne XE possède la ligne d'interruption 0x00. Bien qu'il s'agisse généralement d'une valeur d'interruption valide, la table de routage des interruptions du southbridge de l'AmigaOne XE est définie par défaut sur "0x00 Disabled". Cette table est programmable, mais comme je n'ai pas d'outil sous AmigaOS pour la consulter, je suppose qu'un pont configuré de cette manière ne génère pas d'interruption. Au moins, aucune valeur n'apparaît dans le gestionnaire d'interruptions d'AmigaOS.

En règle générale, l'absence d'interruptions générées par le pont n'est pas une erreur. Les cartes PCIe modernes ne possèdent pas de broches INTx# matérielles et ne génèrent pas d'interruptions de PCI ancien. Elles génèrent plutôt des messages PCIe Assert_INTx/Deassert_INTx. Le pont transparent traduit ces messages reçus de la carte PCIe en interruptions matérielles INTx# pour PCI ancien sur le bus PCI.

La valeur de la ligne d'interruption définie pour le pont indique uniquement le numéro d'interruption que le pont générera pour lui-même (et non pour la carte). J'avoue ne pas savoir si le pont lui-même génère quoi que ce soit. Probablement pas, car le gestionnaire d'interruptions de la Sam440ep-flex est également inexistant.

Ensuite, cela diffère dans la taille du cache : 32 octets pour l'AmigaOne XE 128 octets pour la Sam440ep-flex. C'est la taille du cache qui est utilisée lorsque les transactions d'écriture, d'invalidation et de lecture de mémoire sont terminées. Si le pont lui-même génère ces transactions ou les transmet entre les bus, il doit contenir ce cache. Si le cache est de 0 octet, tout est bien sûr plus lent. La différence de taille de cache est probablement due aux propriétés différentes de l'arbitre PCI. Tous les périphériques PCI de l'AmigaOne XE, s'ils disposent d'une ligne de cache, n'ont que 32 octets.

Nous constatons également que la plupart des autres données sont identiques. Et c'est normal. C'est le même pont.

Nous souhaitons donc configurer une ligne d'interruption sur le pont dans l'AmigaOne XE. J'ai un pont PCI-PCIe dans le port PCI 33 MHz numéro 3 ; d'après la figure 4.1, nous souhaitons donc une valeur de 11 (0x0b). Sachant que cela peut être inutile, mais cela ne devrait pas faire de mal si cela fonctionne sur la Sam440ep-flex. Nous ne toucherons pas à la ligne de cache, 32 octets suffisent pour l'AmigaOne XE.

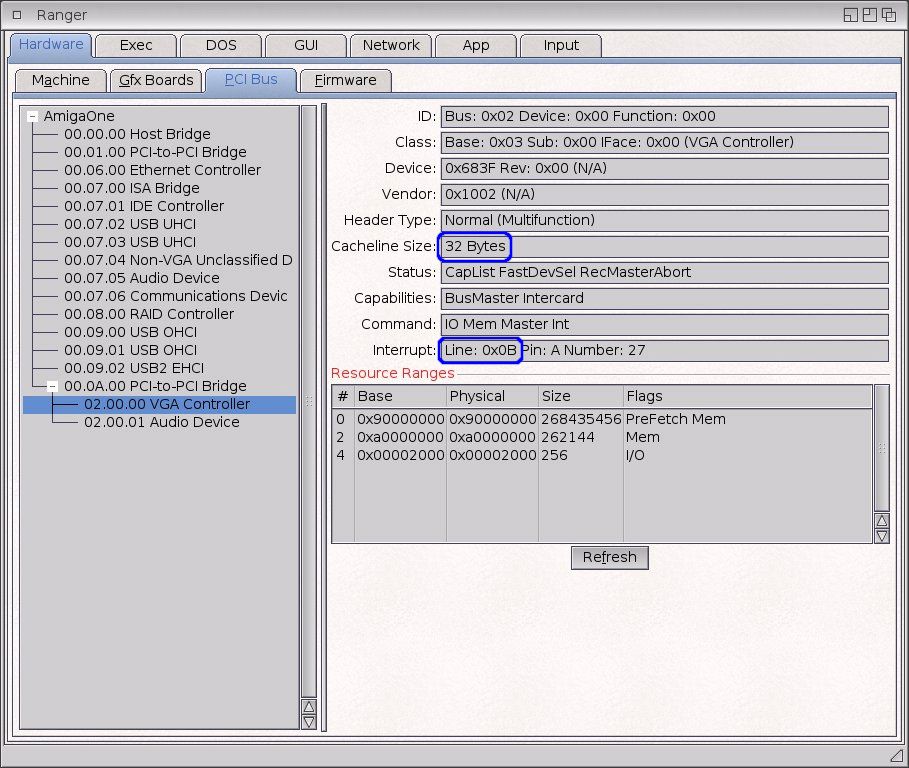

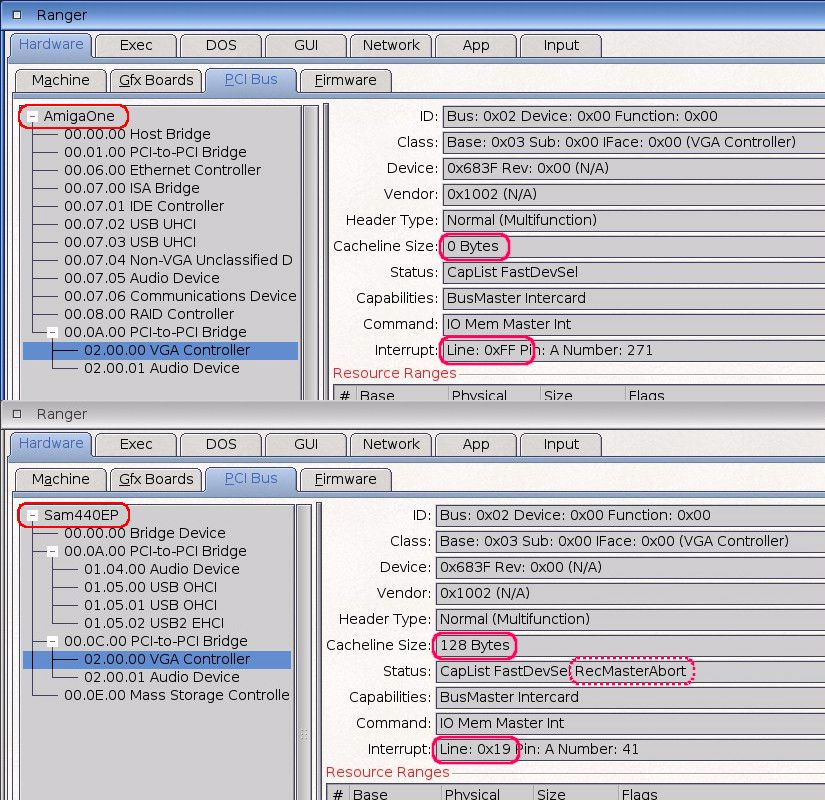

5.2 Comparaison des cartes graphiques derrière le pont dans l'AmigaOne XE et la Sam440ep-flex

Comparons maintenant les données de la carte graphique HD7750 derrière le pont PCIe dans l'AmigaOne XE et le Sam440ep-flex. Encore une fois, ils diffèrent dans la ligne d'interruption : "0xFF" pour l'AmigaOne XE et "0x19" pour la Sam440ep-flex.

Figure 5.2 - comparaison des cartes graphiques AmigaOne XE/Sam440ep-flex

Encore une fois, il existe une différence au niveau de la taille de cache : 0 octet pour l'AmigaOne XE et 128 octets sur la Sam440ep-flex. Et cela est également dérangeant. Cela signifie que l'AmigaOne XE n'utilise pas de cache pour les lectures et écritures en mémoire.

Plus loin dans la case "Status", la Sam440ep-flex dispose de l'option "RecMasterAbort" en plus, mais ignorons-la, c'est un état opérationnel sur le bus.

Nous souhaitons donc redéfinir la ligne d'interruption de la carte dans l'AmigaOne XE sur 11 (0x0b). Selon la spécification du bus PCI, le premier périphérique après le pont correspond à la broche A de la carte pont, donc ici encore 11 (0x0b). La spécification des ponts PCI contient un grand tableau de routage des interruptions. N'hésitez pas à le consulter.

Ensuite, nous allons essayer de définir la valeur de la ligne de cache pour l'AmigaOne XE à 32 octets. Dans l'en-tête, cette valeur est donnée en DWORDS (4 octets), donc la valeur souhaitée sera 32/4 = 8 (0x08).

6. État du bus PCI et ce que nous voulons exactement corriger

Dans notre cas, la position des cartes sur le bus est la suivante :

- Port PCI 33 MHz numéro 1 (adr 00.08.00) : contrôleur SATA.

- Port PCI 33 MHz numéro 2 (adr 00.09.00) : carte réseau 1 GbE.

- Port PCI 33 MHz numéro 3 (adr 00.0A.00) : pont PCI vers PCIe.

- adresse 02.00.00 : carte graphique PCIe.

Pont :

- adresse 00.0A.00, ligne d'interruption = (octet 3Ch dans l'en-tête PCI, voir Figure 4.5) = 0x0b.

- adresse 02.00.00, ligne d'interruption = (octet 3Ch dans l'en-tête PCI) = 0x0b.

- adresse 02.00.00, ligne de cache = (octet 0Ch dans l'en-tête PCI) = 0x08.

C'est facile à dire, mais comment le faire ?

7.1 Commandes U-Boot

Heureusement, dans U-Boot sur AmigaOne XE, nous disposons de quelques commandes puissantes pour travailler avec le bus PCI, que nous pouvons utiliser pour afficher et modifier les paramètres sur le bus PCI :

- pci [bus] [long] - liste courte ou longue des périphériques PCI sur "bus".

- pci header bdf - affiche l'en-tête du périphérique PCI "bus.device.function".

- pci display[.b, .w, .l] bdf [address] [# of objects] - affiche l'espace de configuration PCI (CFG).

- pci next[.b, .w, .l] bdf address - modifie, lit et conserve l'adresse CFG.

- pci modify[.b, .w, .l] bdf address - modifie, incrémente automatiquement l'adresse CFG.

- pci write[.b, .w, .l] bdf address value - écrit à l'adresse CFG.

Commençons par examiner ce que nous allons faire dans U-Boot. Ici, nous entrons dans la ligne de commande. Nous allons d'abord examiner les périphériques sur le bus PCI 0 et le bus 2 :

] pci 00 Scanning PCI devices on bus 0 BusDevFun VendorId DeviceId Device Class Sub-Class _____________________________________________________________ 00.00.00 0x10cc 0x0660 Bridge device 0x00 00.01.00 0x10cc 0x0661 Bridge device 0x04 00.06.00 0x10b7 0x9200 Network controller 0x00 00.07.00 0x1106 0x0686 Bridge device 0x01 00.07.01 0x1106 0x0571 Mass storage controller 0x01 00.07.02 0x1106 0x3038 Serial bus controller 0x03 00.07.03 0x1106 0x3038 Serial bus controller 0x03 00.07.04 0x1106 0x3057 Build before PCI Rev2.0 0x00 00.07.05 0x1106 0x3058 Multimedia device 0x01 00.07.06 0x1106 0x3068 Simple comm. controller 0x80 00.08.00 0x1095 0x3114 Mass storage controller 0x04 00.09.00 0x1033 0x0035 Serial bus controller 0x03 00.09.01 0x1033 0x0035 Serial bus controller 0x03 00.09.02 0x1033 0x00e0 Serial bus controller 0x03 00.0a.00 0x12d8 0xe111 Bridge device 0x04 ] ] pci 02 Scanning PCI devices on bus 2 BusDevFun VendorId DeviceId Device Class Sub-Class _____________________________________________________________ 02.00.00 0x1002 0x683f Display controller 0x00 02.00.01 0x1002 0xaab0 Multimedia device 0x03 |

Ci-dessus, nous voyons notre pont (00.0a.00) et notre carte graphique (02.00.00). Si votre configuration de carte est différente de la mienne, vérifiez ici les adresses PCI correctes.

Examinons maintenant l'en-tête PCI du pont :

] pci header 00.0a.00 vendor ID = 0x12d8 device ID = 0xe111 command register = 0x0007 status register = 0x02b0 revision ID = 0x02 class code = 0x06 (Bridge device) sub class code = 0x04 programming interface = 0x00 cache line = 0x08 latency time = 0x20 header type = 0x01 BIST = 0x00 base address 0 = 0x00000000 base address 1 = 0x00000000 primary bus number = 0x00 secondary bus number = 0x02 subordinate bus number = 0x02 secondary latency timer = 0x00 IO base = 0x21 IO limit = 0x21 secondary status = 0x2000 memory base = 0xa000 memory limit = 0xa000 prefetch memory base = 0x9001 prefetch memory limit = 0x9ff1 prefetch memory base upper = 0x00000000 prefetch memory limit upper = 0x00000000 IO base upper 16 bits = 0x0000 IO limit upper 16 bits = 0x0000 expansion ROM base address = 0x00000000 interrupt line = 0x00 interrupt pin = 0x01 bridge control = 0x0018 ] ] pci display 00.0a.00 00000000: e11112d8 02b00007 06040002 00012008 00000010: 00000000 00000000 00020200 20002121 00000020: a000a000 9ff19001 00000000 00000030: 00000000 00000080 00000000 00180100 ] |

Dans cette liste détaillée et compacte, nous pouvons voir les valeurs de "cache line" (ligne de cache) et de "interrupt line" (ligne d'interruption) mises en évidence par du texte en gras.

Voici ensuite la liste de la carte graphique avec les valeurs en gras :

] pci header 02.00.00 vendor ID = 0x1002 device ID = 0x683f command register = 0x0007 status register = 0x0010 revision ID = 0x00 class code = 0x03 (Display controller) sub class code = 0x00 programming interface = 0x00 cache line = 0x00 latency time = 0x00 header type = 0x80 BIST = 0x00 base address 0 = 0x9000000c base address 1 = 0x00000000 base address 2 = 0xa0000004 base address 3 = 0x00000000 base address 4 = 0x00002001 base address 5 = 0x00000000 cardBus CIS pointer = 0x00000000 sub system vendor ID = 0x1043 sub system ID = 0x0427 expansion ROM base address = 0x00000000 interrupt line = 0xff interrupt pin = 0x01 min Grant = 0x00 max Latency = 0x00 ] ] pci display 02.00.00 00000000: 683f1002 00100007 03000000 00800000 00000010: 9000000c 00000000 a0000004 00000000 00000020: 00002001 00000000 00000000 04271043 00000030: 00000000 00000048 00000000 000001ff |

7.3 Correction des paramètres d'en-tête PCI

Alors, ce qu'U-Boot n'a pas fait, nous allons essayer de le réparer. Si c'est votre première fois, respirez profondément et commençons :

] pci write.b 00.0A.00 3c 0b ] pci display 00.0a.00 00000000: e11112d8 02b00007 06040002 00012008 00000010: 00000000 00000000 00020200 20002121 00000020: a000a000 9ff19001 00000000 00000000 00000030: 00000000 00000080 00000000 0018010b |

Et nous pouvons voir que l'interruption du pont PCIe a pris la valeur souhaitée. Ouf ! Passons à la carte graphique :

] pci write.b 02.00.00 3c 0b ] pci write.b 02.00.00 0c 08 ] pci display 02.00.00 00000000: 683f1002 00100007 03000000 00800008 00000010: 9000000c 00000000 a0000004 00000000 00000020: 00002001 00000000 00000000 04271043 00000030: 00000000 00000048 00000000 0000010b |

...nous voyons que la ligne d'interruption et la ligne de cache ont changé pour la carte graphique.

Ensuite, démarrez simplement le système et voilà :

Alors ça a marché !

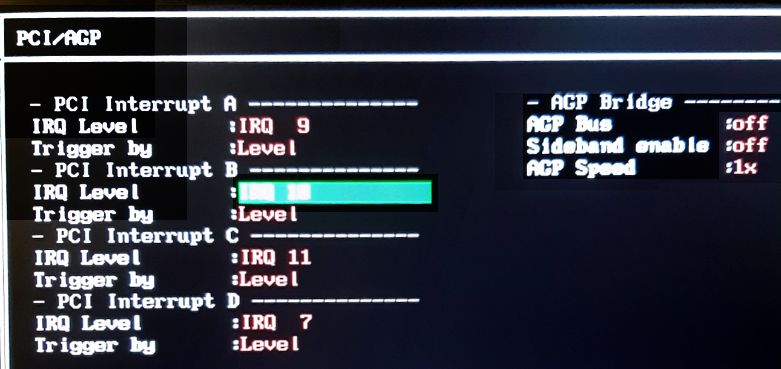

8. Utilisation du menu U-Boot PCI/AGP

Il serait également possible d'utiliser d'autres options d'U-Boot, d'autres paramètres de ligne d'interruption.

Dans le menu "PCI/AGP", nous pouvons définir le "IRQ Level" (niveau IRQ) pour les interruptions PCI en plus du pont AGP. Modifiez donc l'affectation des lignes avec différentes valeurs. Pour chacune des quatre broches physiques du contrôleur (dans le menu "Interruption PCI A = PIRQ A#", etc.), il est possible de sélectionner l'une des valeurs suivantes : 9, 10, 11, 13 ou 7.

Jusqu'à présent, nous avons travaillé avec les paramètres par défaut, comme indiqué dans la figure 8.1. Si vous modifiez les paramètres par simple décalage (par exemple, PCI int A = 10, B = 11, C = 7, D = 9), les lignes et les numéros d'interruption changeront, mais du point de vue de l'utilisateur et du système, cela n'a aucune importance. Cela ne nous aide pas.

Affecter toutes les interruptions physiques aux mêmes lignes d'interruption n'est ni raisonnable ni très logique. Plusieurs périphériques auraient simplement le même numéro d'interruption. Et si vous utilisez la valeur 13 (0xD) pour l'une des interruptions, rien ne se passe - rien n'est affecté sur 13. Dans la table de routage du contrôleur, l'interruption 13 est marquée comme "Reserved" (Réservée) et je ne sais pas exactement à quoi elle sert. En réalité, aucune interruption 29 (= 13+16) n'apparaît dans le gestionnaire d'interruptions d'AmigaOS.

Et ce que nous pouvons également définir dans le menu U-Boot, c'est comment l'interruption sera générée :

- "Trigered by level" (Déclenché par niveau) : l'interruption est générée en continu et seule sa résolution en met fin. Normalement, ce paramètre est correct. L'interruption est résolue tant que le périphérique la signale.

- "Triggered by edge" (Déclenché par front) : l'interruption n'est générée qu'une seule fois (lorsque le signal physique augmente). Il peut donc arriver que personne ne résolve l'interruption. Ce paramètre n'est généralement pas utilisé. Il ne doit être utilisé que si le système se bloque lors de la gestion des interruptions, c'est-à-dire si le périphérique est submergé de requêtes et que le pilote n'est pas conçu de manière optimale.

9. Automatisation

Nous pouvons définir l'interruption correcte sur une carte graphique PCIe. Mais il serait peu pratique de ressaisir les commandes d'écriture PCI à chaque démarrage. On s'en lasserait vite. Heureusement, nous pouvons automatiser cela. Sous AmigaOS, nous créons une nouvelle variable d'environnement, "pcifix", via le Shell. Vous pouvez bien sûr également le faire depuis la ligne de commande U-Boot, mais cette méthode est plus pratique.

> nvsetvar pcifix "pci write.b 00.0a.00 3c 0b; pci write.b 02.00.00 3c 0b; pci write.b 02.00.00 0c 08" |

Et puis on vérifie :

> nvgetvar pcifix pci write.b 00.0a.00 3c 0b; pci write.b 02.00.00 3c 0b; pci write.b 02.00.00 0c 08 |

Nous ne pouvons alors entrer qu'une seule commande à chaque démarrage dans la ligne de commande U-Boot :

] run pcifix |

Et nous avons réussi à le réparer sans risquer une faute de frappe.

Si le résultat de la correction de la configuration PCI nous convient et que les tests sont terminés, nous procéderons à une automatisation complète. Modifions la variable "menuboot_cmd" comme suit :

> nvsetvar menuboot_cmd "run pcifix; boota; boota; boota" |

Cela démarrera le correctif automatiquement à chaque démarrage d'AmigaOS. Mais n'oubliez pas de remettre cette variable à son état d'origine lorsque vous retirez la carte PCIe de votre Amiga.

10. Autres versions d'U-Boot

Tous les tests ont été effectués avec la dernière version officielle d'U-Boot d'Hyperion, c'est-à-dire la 1.1.1. Cependant, d'autres versions étaient disponibles pour les bêta-testeurs mais n'ont jamais été officiellement publiées. Outre le fait que les versions supérieures devraient permettre le démarrage à partir d'autres cartes PCI (SiI3114, SiI35121 ), il existe d'autres différences pour nous :

Tableau 10.1 - les différentes versions d'U-Boot

11. Conclusion

Après avoir ajusté manuellement les interruptions et la ligne de cache, la vitesse de la carte graphique n'a augmenté que légèrement. MPlayer a été accéléré de deux secondes : de 307,905 à 305,879 secondes. ioquake3 est passé de 21,5 à 21,9 ips. En fonctionnement normal, l'utilisateur ne remarquera rien. J'imagine qu'il faudrait un processeur plus rapide que mon PowerPC G4 à 800 MHz pour accentuer les différences. Mais nous pouvons déjà être satisfaits d'avoir corrigé les bogues d'U-Boot et de mieux comprendre les choses.

Ce qui est bien, c'est qu'avant la modification, le débogage série dans RadeonHD ressemblait à ceci :

... RadeonHD.chip (0): RadeonHD card successfully opened RadeonHD.chip (0): UBoot has not initialized the graphics card's interrupt line. Disabling interrupts. RadeonHD.chip (0): Please upgrade your UBoot firmware. a1ide.device 53.22 (28.6.2017) [a1ide/dev_init] a1ide_timeout : '10', adjusted ata timeout to 10 ... |

Et après notre modification, cela ressemble à ceci :

... RadeonHD.chip (0): RadeonHD card successfully opened a1ide.device 53.22 (28.6.2017) [a1ide/dev_init] a1ide_timeout : '10', adjusted ata timeout to 10 ... |

Autre avantage important : nous pouvons utiliser les "cartes combo" dans notre AmigaOne XE. Ces cartes contiennent un pont PCI vers PCI et plusieurs périphériques en aval. Par exemple, SATA et Firewire ou SATA et USB. En réalité, la plupart d'entre elles n'ont des pilotes que pour Linux, mais nous savons maintenant comment les faire fonctionner. Cela fonctionne de la même manière que nos cartes graphiques : aucune fonction derrière le pont n'est initialisée par U-Boot. Il suffit donc de définir l'interruption correcte.

Rebus - Explication du diagramme PCI (du début de l'article)

Vous ne trouverez donc pas ici de solution, juste une réflexion. Selon la spécification PCI, si des périphériques 33 et 66 MHz sont regroupés sur un même bus, celui-ci fonctionne entièrement à 33 MHz. Ainsi, le pont PCI-vers-PCI 00.01.00, qui sépare le bus PCI 1 (66 MHz), ne fonctionnerait qu'à 33 MHz. La carte graphique peut donc être aussi rapide qu'elle le souhaite, mais le débit de transfert peut alors être limité à 133 Mo/s (bus PCI 0, 33 MHz).

Un merci spécial à Evillord68 pour son aide.

|

|